In my previous, actually first post about ASIC design with open source tools, I talked about the first automation step, which is synthesis and its output, which is a netlist:

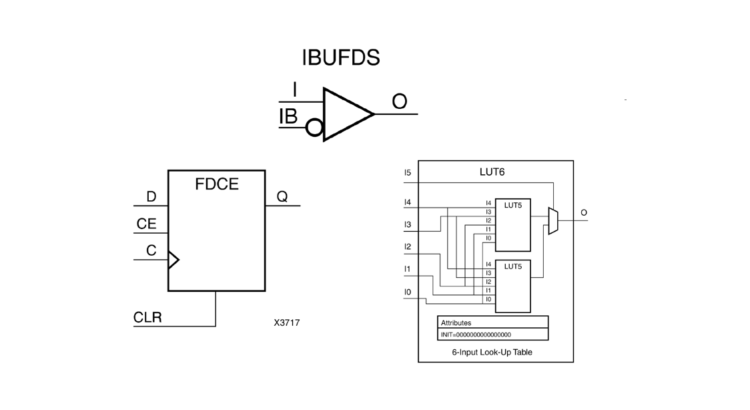

We saw that an N-bit Verilog counter code is synthesized into logic cells and nets connecting them. File formats for this information in Vivado are Verilog(.v) and EDIF(.edn). I also showed netlist files and there were different modules inside these files such as IBUF, BUFG, LUT3, LUT4, OBUF and FDCE. As Vivado synthesis tool aims for a Xilinx FPGA defined when project is created, basic logic cells are elements inside the FPGA architecture such as LUTs and FFs for logic and BUFs for I/O and clock signals. But, how synthesis tool decides which elements to select? Well, here comes the “library”.

Xilinx has a lot of different FPGA families. Artix7, Kintex7, Virtex7 and Zynq7000 were and are still very poppular FPGA families even though new families such as ultrascale and ultrascale+ arose. Before, there were Spartan6 and Spartan3. I don’t remember before Spartan3 family, I am not that old ! However, I am old enough to used Spartan3 family FPGAs with famous Xilinx ISE tool. Nowadays, LUTs with 6-inputs seems normal to everyone, while in Spartan3 times it was only 4-inputs. There were not any DSP48 primitives but MULT18x18s. These are actually architecture properties of different FPGA families of Xilinx and these architecture primitives sets are called as “library”.

Synthesis process is proprietary and secret for companies. However, libraries are published and documented. In the next posts, we will look at Yosys open source synthesis tool, in which we can dive more into how synthesis procedure works. But for now, we will only analyze different FPGA architectures and libraries for Xilinx families.

Spartan-3E family is a very old FPGA family, even finding documents for Spartan-3E is not that easy. Luckily I found “Spartan-3E Libraries Guide for HDL Designs”:

https://my.eng.utah.edu/~cs3710/xilinx-docs/spartan3e_hdl.pdf

This document and the document I will show soon (“Xilinx Vivado Design Suite 7 Series FPGA Libraries Guide”) have similar structures:

The document first talks about different design techniques as shown above. Then functional categories:

Let’s look at Arithmetic Functions:

I told you, there were no DSP48 before! So when you multiply two signals in an HDL code and synthesize it for a Spartan-3E family FPGA in Xilinx ISE, the tool will select a MULT18X_ element and use it if there is any left inside the FPGA. I added some other categories from Spartan-3E for you to compare new FPGA architectures:

As you see the LUT can only has 4-input for Spartan-3E FPGAs.

If you select a Spartan6 family FPGA, this time you have a new library named “Spartan-6 Libraries Guide for HDL Designs”:

https://www.xilinx.com/htmldocs/xilinx14_7/spartan6_hdl.pdf

We can see that now there is LUT5 and LUT6 in Slice/CLB primitives category:

Also we have DSP48 instead of MULT18X_:

Xilinx 7 series FPGAs has also a different library:

https://docs.xilinx.com/v/u/2012.2-English/ug953-vivado-7series-libraries

We can see that the element having DSP functionality changed from DSP48A1 to DSP48E1:

The point is, it is very important to know the logic elements or primitives of the library whenever you want to synthesize an HDL for an FPGA, whether it is from Xilinx, Intel or any other.

But what about if you write HDL not for an FPGA but an ASIC? Do we still have LUTs? How about arithmetic elements? Do we have DSP48 or MULT18X18? What about high speed serial interfaces? In Xilinx for example we have GTPE2_CHANNEL and GTP2E_COMMON, ISERDESE2 or IDELAYE2. The tool automatically infer these primitives, what about if we aim for an ASIC? Do we need a kind of library such as Xilinx provides us for each FPGA family they produce?

Hope we can find answers these questions in next posts in this series.

Regards,

Mehmet Burak AYKENAR

You can connect me via LinledIn: Just sent me an invitation