In the previous post, I was able to harden a RISC-V based SoC in Openlane. There were 3 methods to harden the chip according to Efabless documentation and I utilized the first method, which was hardening the macros first, then integrating all the macros in the top module by instantiating them, while there must be […]

Kategori: OPEN SOURCE ASIC DESIGN

This page includes information about how to design ASIC (or VLSI or CHIP in some literature) with open source tools included in OpenLane project.

RISC-V Based SoC Design with Open-Source Openlane IC Design Tool

This is the second post for the series of open-source IC design flow. The first post talked about how to use open-source tools, namely Openlane to harden a RISC-V CPU core, in which we generated GDS outputs of the CPU core. The famous PicoRV32 RISC-V core is chosen for this purpose. You can find the […]

Open-Source IC Design Flow for an Open-Source RISC-V Core

I can say I am more of an RTL design engineer. I had a lot of experience in RTL design deployed in FPGA systems before gaining interest in IC design. In FPGA, or now also in SoC (Processing System [PS] + Programmable Logic [PL]) you write your RTL code in one of the HDLs, namely […]

Synthesis N-bit Counter with Open-Source Yosys Synthesizer

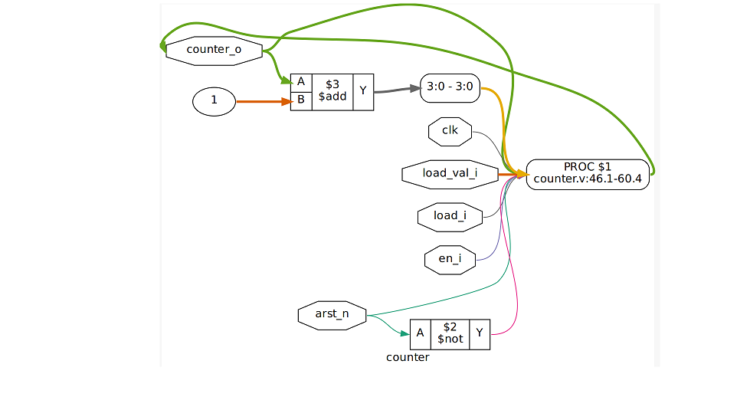

In this post, I will show how to install Yosys open source synthesizer and how to use basiccommands. Also I will synthesize N-bit counter that I have written in the first post of this series. Yosys works on Linux environment. If you are a Windows user and want to use Yosys, you needCygwin to emulate […]

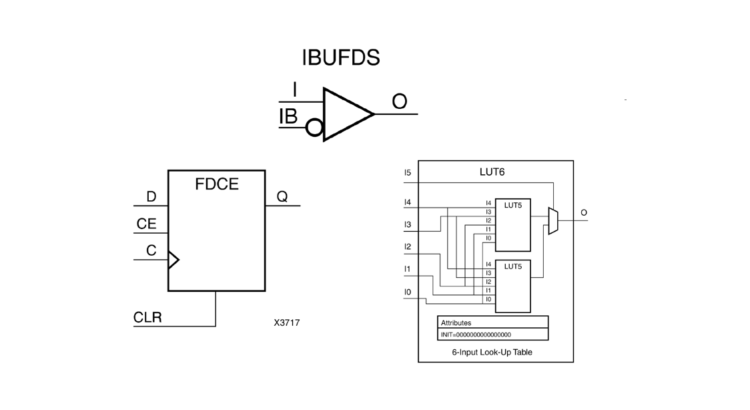

FPGA Synthesis | Xilinx Spartan-3E/6 and 7-Series Library Analysis

In my previous, actually first post about ASIC design with open source tools, I talked about the first automation step, which is synthesis and its output, which is a netlist: https://www.mehmetburakaykenar.com/first-step-to-asic-design-synthesis-netlist-verilog-counter-example-on-vivado/254/ We saw that an N-bit Verilog counter code is synthesized into logic cells and nets connecting them. File formats for this information in Vivado […]

First Step to ASIC Design: Synthesis & Netlist | Verilog Counter Example on Vivado

This is the first post on this subject: Open Source ASIC Design. I am interested in ASIC design recently. For years (>10) I designed digital circuits with VHDL. At the beginning of this year (2022), I started working in Yongatek Microelectronics company, located in Istanbul and Ankara in Turkey. Here WE {I adapted quickly and […]