In my latest post, I talked about AXI-Stream protocol and showed a running design on Zedboard utilizing AXI-Stream FIFO and ILA: https://www.mehmetburakaykenar.com/what-is-axi-stream-protocol-axi-stream-fifo-tutorial-with-vivado-and-vitis-running-on-zynq-zedboard/377/ Today, I will show how to create a custom AXI-Stream peripheral in Vivado with VHDL. The use case is an arithmetic co-processor, where the arithmetic operation of the co-processor will be selected between […]

Etiket: xilinx

What is AXI-Stream protocol? AXI-Stream FIFO Tutorial with Vivado and Vitis, running on ZYNQ, ZEDBOARD

So far in my blogs I utilized Zynq PS DMA and AXI CDMA IPs to move data between DDR RAM, on-chip ram (OCM) and PL Block RAM (BRAM). I have designed Vivado HW and Vitis SW parts and showed latency results for these two scenarios, which you can find at the links all the details: […]

XILINX ZYNQ AXI Central DMA (CDMA) On-Chip Memory (OCM), DDR3 RAM and PL Block RAM Data Transfer Performances

It has been a long time that I posted on my webpage related to Digital Design and SoC concepts. My last post was related to evaluating data transfer rates between OCM, DDR3 RAM and PL Block RAM by utilizing PS DMA of Processing System of the Zynq SoC. Please visit the related post for details: […]

XILINX ZYNQ PS DMA | On-Chip Memory (OCM), DDR3 RAM and PL BRAM Data Transfer Performances

It has been a long time that I posted on my webpage related to Digital Design and SoC concepts. This post will be related to Zynq Processing System (PS) DMA usage example and performance analysis on data transfer between DDR3 RAM, OCM and PL Block RAM. I will provide both PL and PS designs and […]

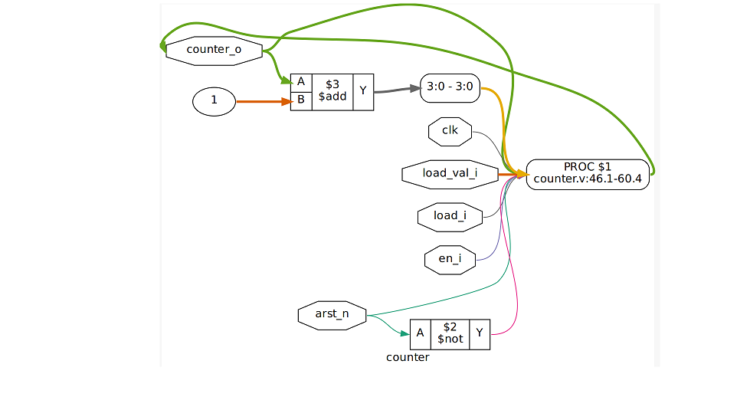

Synthesis N-bit Counter with Open-Source Yosys Synthesizer

In this post, I will show how to install Yosys open source synthesizer and how to use basiccommands. Also I will synthesize N-bit counter that I have written in the first post of this series. Yosys works on Linux environment. If you are a Windows user and want to use Yosys, you needCygwin to emulate […]

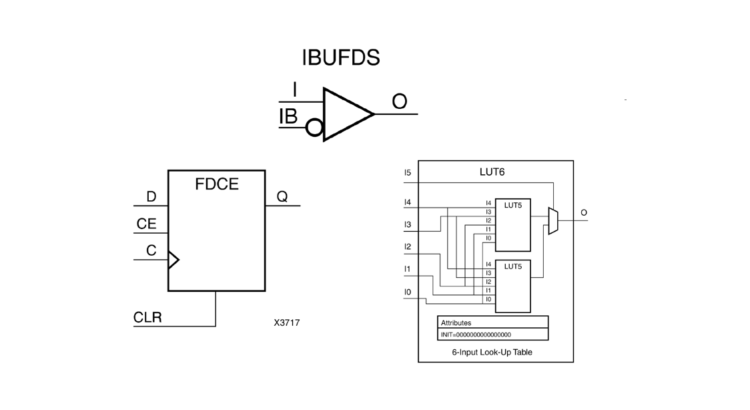

FPGA Synthesis | Xilinx Spartan-3E/6 and 7-Series Library Analysis

In my previous, actually first post about ASIC design with open source tools, I talked about the first automation step, which is synthesis and its output, which is a netlist: https://www.mehmetburakaykenar.com/first-step-to-asic-design-synthesis-netlist-verilog-counter-example-on-vivado/254/ We saw that an N-bit Verilog counter code is synthesized into logic cells and nets connecting them. File formats for this information in Vivado […]

HOW TO CREATE an AXI4-FULL CUSTOM IP with AXI4-LITE and UART INTERFACES in VIVADO

In this post, I will show how to create a custom IP in Vivado, which has an AXI4-Lite interface, an AXI4-Full interface and a UART interface. Long time ago, when I first met with Zynq and a Microblaze SOM, I started learning how to generate a custom AXI4-Lite IP from Mr. Adam Taylor’s Microzed Chronicles blog. Now it is my time to contribute to the digital design community by showing AXI4-Full IP generation and an example code utilizing a UART interface.

VERIFICATION of A CUSTOM AXI4 LITE IP USING UVVM

If you are using or plan to use Xilinx Zynq (or any other SoC), most probably you will encounter creating your own IP modules and the poppular way to connect your IP to Processing System is via AXI4 protocol.

KALMAN FILTER IMPLEMENTATION on ZYNQ PS (ARM CORTEX-A9) and LATENCY MEASUREMENTS

This post is about Kalman filter implementation with C++ using Eigen library and running it on Xilinx Zynq SoC PS part. Beware! Latency measurements will show the reader some good info!

VERIFICATION of the HIGH SPEED UART TRANSCIEVER with FIFO CDCs USING UVVM

In my last post, I utilized FIFOs for CDC synchronization for a high speed UART transciever system. To remeber, there were a UART receiver and a UART transmitter, which run at 250 MHz and the internal logic runs at 100 MHz. There are FIFOs between two clock domains, where ona side of the FIFO runs […]